Hardware-in-the-loop

Professional hardware-in-the-loop technique to test your control installed in the final target

The Hardware-in-the-loop activity is managed in EicasLab by the Hardware-in-the-loop operative sub-mode that allows the user to predispose any testing scenario which can be useful for testing and validating the user application.

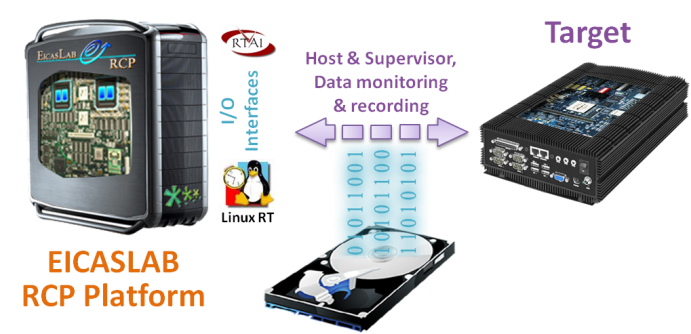

The control algorithms run on the final target suitable connected with the EicasLab RCP platform, in which the simulated plant is executed. The overall trial is managed through the EicasLab HIL Manager tool running on the EicasLab RCP platform. During the Hardware-in-the-loop execution, data can be visualized on the HIL Manager tool GUI and they can also be recorded on the disk for a further post processing analysis.

The EicasLab Assisted Compiling Process automatically generates the whole real-time code, consisting in both Application Software and Basic Software, necessary for performing the Hardware-in-the-loop activity. For generating such a real-time code the Assisted Compiling Process calls:

- ACG for AS feature provided by the ACGAS module.

- ACG for HIL feature provided by the HIL/FVT module.

- ACG for HW Target provided by the HW Target module.

Hardware-in-the-loop Highlights

- Enable Hardware‐in‐the‐loop process and final validation test in EicasLab

- Powerful multi‐threading and multi‐core programming techniques

- Automatic code generation for different HW target families

- Easy configuration of HW interfaces and control activities real ‐ time scheduling

- EICASLAB RCP Platform used for host & supervisor PC, data monitoring and data recording