excellence and passion in automatic control design

## A/D and D/A Converters in $EICASLAB^{TM}$

Welcome to Innovation

Via Vincenzo Vela, 27 10128 Torino - ITALY (IT) Tel. +39 011 56 23 798 +39 011 56 23 088 Fax +39 011 43 60 679

excellence and passion in automatic control design

## TABLE OF CONTENT

- General description of the A/D and D/A converters

- The Library Converters

- The ANSI C Converters

- The scheduling of the A/D and D/A converters

The A/D and D/A **converters** are the interface between **analogical** and **digital** signals.

There are then 2 types of converters:

- the analogical  $\rightarrow$  digital (A/D) converters (**sensors**),

- the digital  $\rightarrow$  analogical (D/A) converters (**actuators**).

All the digital signals are characterized by a **quantization level.** The converters need to know it for working: it is their fundamental parameter.

## The A/D and D/A connections in EICASLAB

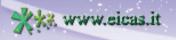

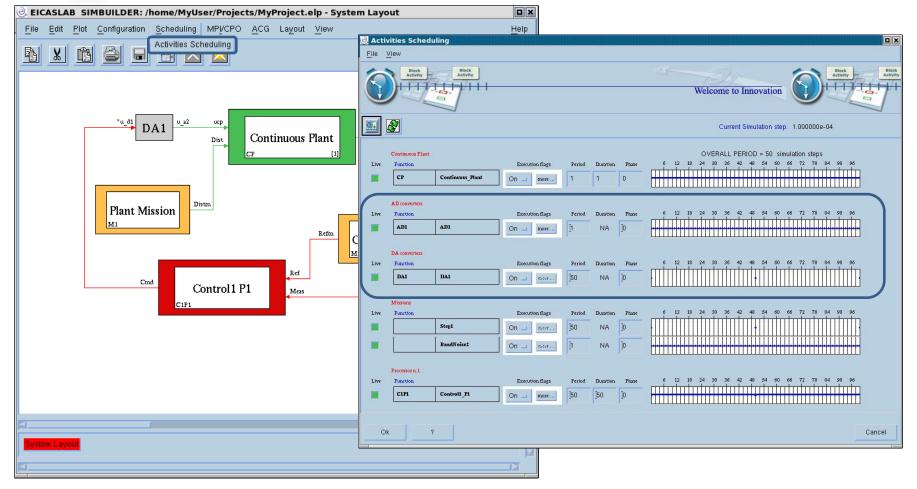

In EICASLAB the **Continuous Plant** block works on analogical data while all the other blocks use digital data.

To connect a Continuous Plant to any other block it is necessary to insert between them the A/D and D/A converter blocks that translate the analogical signals belonging to the Continuous Plant (analogical data) into discrete signals (discrete data) and vice versa.

www.eicaslab.com

excellence and passion in automatic control design

## The A/D and D/A converter blocks in EICASLAB

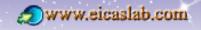

The converters are blocks belonging to the **I/O Devices** library. They can be inserted in:

- the System Layout (they are available in the *I/O Devices* library of the System Library window)

- the Hybrid Plant Layout (they are available in the *I/O Devices* library of the Hybrid Library window)

excellence and passion in automatic control design

# The Programming modes of the A/D and D/A converters

You can program the A/D and D/A converters in two ways:

using predefined models that you can customize setting suitable parameters (**Library Converters**),

using the ANSI C language (**ANSI C Converters**).

excellence and passion in automatic control design

A/D> D/A>

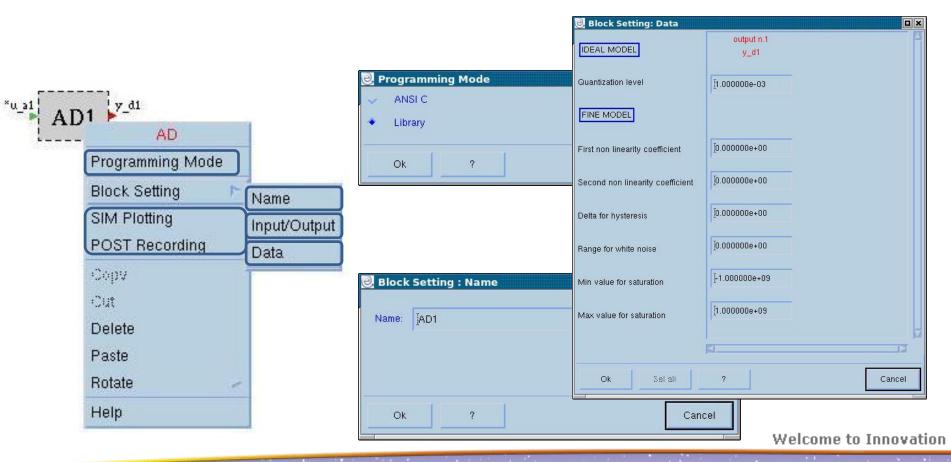

### The Library Converters Associated popup menu

When you insert a converter in your project it is, by default, a Library Converter.

**EICAS** Automazione S.p.A.

excellence and passion in automatic control design

8

#### **EICAS** Automazione S.p.A.

excellence and passion in automatic control design

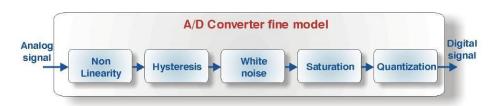

#### The Library Converters

The pre-defined model for A/D converters (1)

#### Ideal Model:

characterised only by the quantization level.

Fine Model:

models the measurement errors:

- non linearity,

- hysteresis,

- white noise,

- saturation.

excellence and passion in automatic control design

#### •A/D> •D/A>

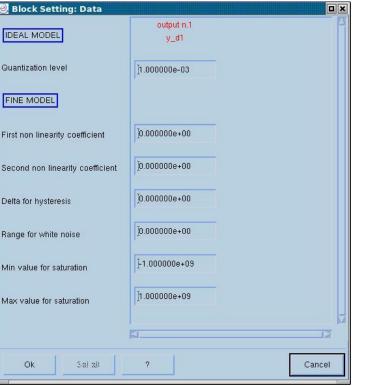

#### **The Library Converters**

## The pre-defined model for A/D converters (2)

| 🧕 Block Setting: Data            |                    |        |

|----------------------------------|--------------------|--------|

| IDEAL MODEL                      | output n.1<br>y_d1 | X      |

| Quantization level               | 1.000000e-03       | ]      |

| FINE MODEL                       |                    |        |

| First non linearity coefficient  | 0.000000e+00       |        |

| Second non linearity coefficient | 0.000000e+00       | ]      |

| Delta for hysteresis             | j0.000000e+00      | ]      |

| Range for white noise            | )0.000000e+00      | ]      |

| Min value for saturation         | -1.000000e+09      |        |

| Max value for saturation         | 1.000000e+09       |        |

|                                  | KI                 | II     |

| Ok Sel ali                       | ?                  | Cancel |

#### Quantization:

divides the measure for the quantization value.

#### Non Linearity:

it adds to the measure 'y' the term 'a sin(y b)' where 'a' and 'b' are respectively the first and the second non linear coefficients;

#### Hysteresis:

it models the behaviour of incremental encoders. It works by verifying the difference between the new measure and the old one, decreasing/increasing the new measure if the difference is greater/minor than a factor *delta*;

#### White noise:

it adds to the measure a signal described by an uniform distribution with a specific *range*;

#### Saturation:

applies an upper and a lower limit to the measure;

A/D> D/A>

## **EICAS** Automazione S.p.A.

excellence and passion in automatic control design

#### The Library Converters

## The pre-defined model for A/D converters (3)

\*u\_a1 \*u\_a2 AD1 y\_d1 y\_d2

An A/D and D/A converter block can have more inputs and outputs.

For complying the pre-defined model the number of outputs must be equal to the number of inputs.

Every input/output can be customized having its own model parameters.

ww.eicas.it

| Block Setting: Data              | output n.1<br>y_d1 | output n.2<br>y_d2[0]                  | output n.3<br>y_d2[1] |            |

|----------------------------------|--------------------|----------------------------------------|-----------------------|------------|

| Quantization level               | 1.000000e-03       | 1.000000e-03                           | 1.000000e-03          |            |

| FINE MODEL                       | Set All            |                                        | ×                     |            |

| First non linearity coefficient  |                    | racteristics independent<br>ter values |                       |            |

| Second non linearity coefficient | 🗸 All parameter v  | alues equal to the ones                | of output n.1         |            |

| Delta for hysteresis             |                    |                                        |                       |            |

| Range for white noise            | Ok                 | 7                                      | Cancel                |            |

| Min value for saturation         |                    | 1.000000e+09                           | ¥-1.000000e+09        |            |

| Max value for saturation         | ž1.000000e+09      | 1.000000e+09                           | 1.000000e+09          |            |

|                                  | <br> 21            |                                        |                       | <b>E</b> 1 |

| Ok Set all                       | ?                  |                                        |                       | Cancel     |

A/D> D/A>

### **EICAS** Automazione S.p.A.

excellence and passion in automatic control design

#### The Library Converters

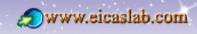

## The pre-defined model for D/A converters

| 🥑 Block Setting: Data            |                      |

|----------------------------------|----------------------|

| IDEAL MODEL                      | output n.1<br>u_a2   |

| Quantization level               | <u>]1.000000e-03</u> |

| FINE MODEL                       |                      |

| First non linearity coefficient  | 0.000000e+00         |

| Second non linearity coefficient | j0.000000e+00        |

| Delta for hysteresis             | j0.000000e+00        |

| Range for white noise            | <u>10.000000e+00</u> |

| Min value for saturation         | 1.000000e+09         |

| Max value for saturation         | [1.000000e+09        |

|                                  | لم<br>در             |

| Ok Sei ali                       | ? Cancel             |

Ideal Model:

characterised only by a quantization level.

Fine Model:

considers also other phenomena:

- saturation.

- non linearity,

- white noise,

- hysteresis.

A/D> D/A

## **EICAS** Automazione S.p.A.

excellence and passion in automatic control design

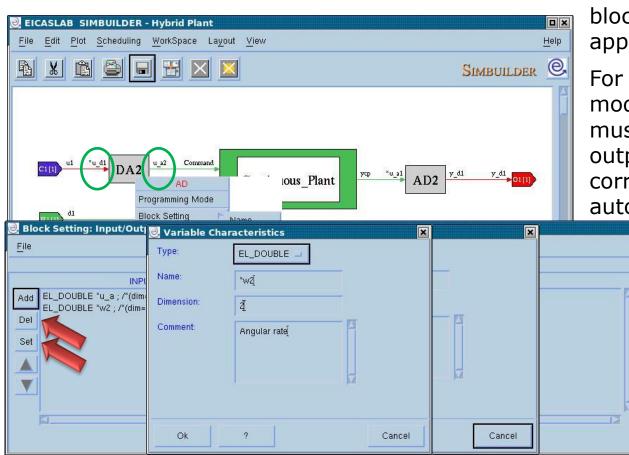

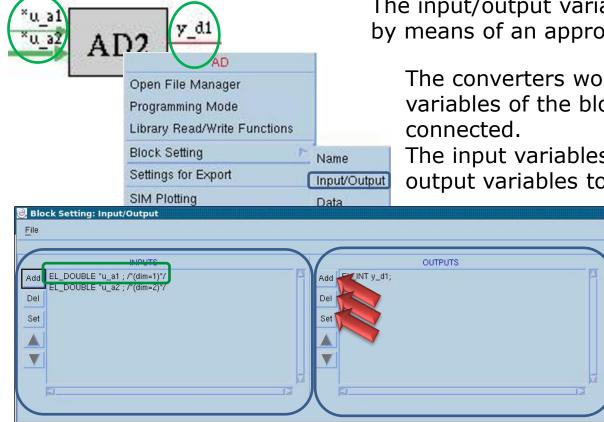

## The Library Converters The Input/Output variables (1)

The input/output variables of the block are defined by means of an appropriate window.

For complying the pre-defined model the number of outputs must be equal to the number of outputs: if you add an input a corresponding output is automatically added.

The input/output variables are ANSI C variables .

Welcome to Innovation

ww.eicas.it

13

A/D> D/A>

#### **EICAS** Automazione S.p.A.

excellence and passion in automatic control design

## The Library Converters The Input/Output variables (2)

| eiCASLAB SIMBUILDER: /home/MyUser/MyProject.elp - System Layou                                                         | t                      |

|------------------------------------------------------------------------------------------------------------------------|------------------------|

| , <u>F</u> ile <u>E</u> dit <u>Plot</u> <u>Configuration</u> <u>Scheduling</u> MPI/CPO <u>A</u> CG Layout <u>V</u> iew | Help                   |

|                                                                                                                        | Simbuilder             |

| DA1 y_3 Command<br>Continuous_Plant                                                                                    | AD1 <sup>y_d</sup>     |

| ළ Block Setting: Input/Output<br>File                                                                                  |                        |

|                                                                                                                        |                        |

| INPUTS                                                                                                                 | OUTPUTS                |

|                                                                                                                        | aτ y_d;<br>aτ y_d1[2]; |

| JSN.                                                                                                                   | 1.4                    |

The converters work directly on the output variables of the blocks to which they are connected.

Any quantity has to be measured when it is available (every measure corresponds to a precise measuring time).

The input variable is then a pointer to the output variable to which it is connected (e.g.: variable  $*u_a$ ).

A/D> D/A>

#### **EICAS** Automazione S.p.A.

excellence and passion in automatic control design

## The Library Converters SIM plotting and POST recording

You can select the input, output, and state variables for plotting and recording them during the simulations.

|        | AD        |

|--------|-----------|

| Progra | mming Mod |

| Block  | Setting   |

| SIM PI | otting    |

| POST   | Recording |

| Copy   |           |

| Cut    |           |

| Delete |           |

| Paste  |           |

| Rotate |           |

| Help   |           |

www.eicas.it

| Input         |                |                       |

|---------------|----------------|-----------------------|

| ■ u_a[1]      |                |                       |

| 📕 w2[2]       | e SIM Plotting | Area(1-6) N(1-4)      |

| Output        | u_a(0)         | þ þ                   |

| ■ y_d         | w2[0]          | j2 [1                 |

| ■ y_d1[2]     | w2[1]          | 12 12                 |

| States        | Output         | Area(1-6) N(1-4)      |

| meas.of:w2[2] | y_d            | <u>1</u>              |

|               | y_d1[0]        | <b>]5</b>             |

|               | y_d1[1]        | <b>]</b> 5 <b>]</b> 2 |

|               | States         | Area(1-6) N(1-4)      |

|               | meas.of:u_a    | I                     |

|               | meas.of:w2[0]  | I                     |

|               | meas.of:w2[1]  |                       |

excellence and passion in automatic control design

#### **EICAS** Automazione S.p.A.

excellence and passion in automatic control design

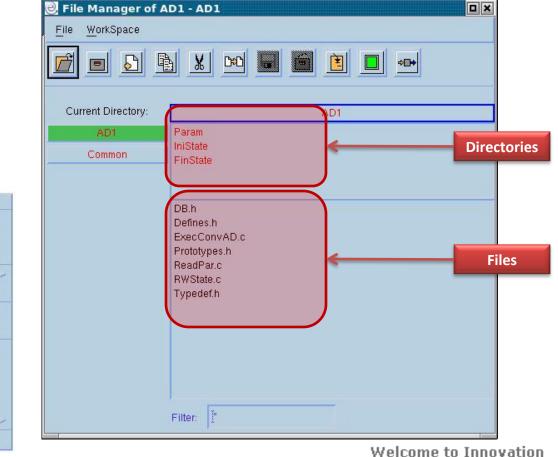

#### The Converter programmed with ANSI C language

The Converter file manager

The Converter programmed with ANSI C language has its own file manager through which it is possible to program the block.

EICASLAB provides a pre-organised structure: a set of template files subdivided in:

- data files,

- header files,

• ANSI C files, that you can write and customize in order to implement your block.

| Open F   | ile Manager     |       |

|----------|-----------------|-------|

| Program  | nming Mode      |       |

| Library  | Read/Write Func | tions |

| Block S  | etting          | 1     |

| Settings | for Export      |       |

| SIM Plo  | itting          |       |

| POST R   | Recording       |       |

| Copy     |                 |       |

| Cut      |                 |       |

| Delete   |                 |       |

| Paste    |                 |       |

| Rotate   |                 | -     |

**EICAS** Automazione S.p.A.

excellence and passion in automatic control design

#### The Converter programmed with ANSI C language The header files

File Manager of AD1 - AD1 WorkSpace File X DeD È \* **Current Directory:** Common AD1 Common.c Common.h Filter: ]\*

Header files of the pre-organised structure that are written by the user.

| Defines.h    | Definition of<br>user constants                   |

|--------------|---------------------------------------------------|

| Typedef.h    | Definition of user<br>structures                  |

| DB.h         | Definition / declaration of user variables        |

| Prototypes.h | Declaration of<br>the function prototypes         |

| Common.h     | Available for all the blocks programmed in ANSI C |

**EICAS** Automazione S.p.A.

excellence and passion in automatic control design

## The Converter programmed with ANSI C language

#### **Initialization functions**

| Name    | Description                                                                                                  | C File       |   |

|---------|--------------------------------------------------------------------------------------------------------------|--------------|---|

| AD#_Exe | Executes all the operations that the activity must perform each time it is scheduled and updates its outputs | ExecConvAD.c | ; |

Welcome to Innovation

www.eicas.it

**EICAS** Automazione S.p.A.

excellence and passion in automatic control design

#### The Converter programmed with ANSI C language Final functions

| Name           | Description              | C File       | Data File       |

|----------------|--------------------------|--------------|-----------------|

| AD#_Fin        | User final function      | ExecConvAD.c |                 |

| AD#_WriteState | Final state file writing | RWState.c    | ConvAD.finstate |

### **EICAS** Automazione S.p.A.

excellence and passion in automatic control design

#### The Converter programmed with ANSI C language

#### **Data file management**

| /************************/<br>void. AD@_ReadPar(FILE *fp)<br>/*                                                                                                                          | File WorkSpace              |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----|

|                                                                                                                                                                                          |                             |    |

|                                                                                                                                                                                          | 🖻 🗉 🔉 🛰 🗠 🖬 🗃 💷 🚥           |    |

| OUTPUTS:<br>value of the AD@ parameters                                                                                                                                                  | Current Directory: FinState |    |

| OBJECTIVES:<br>The function can read the parameters of the AD@ module from the file ConvAD.par.                                                                                          | AD1                         |    |

| All the parameters should be defined in:<br>DB.h. database of the AD@ Module                                                                                                             |                             |    |

| SCHEDULE:<br>The function is called by the EICASLAB simulator nucleus,<br>once at the beginning of the simulation session,<br>before the functions AD@_ReadState and AD@_Ini.<br>*/<br>{ | ConvAD.finstate             |    |

| return;<br>}<br>/********************/                                                                                                                                                   |                             |    |

|                                                                                                                                                                                          |                             |    |

|                                                                                                                                                                                          | Filter:                     | 31 |

|                                                                                                                                                                                          |                             |    |

| Filter:                                                                                                                                                                                  |                             |    |

#### **EICAS** Automazione S.p.A.

excellence and passion in automatic control design

#### The Converter programmed with ANSI C language

#### **The Library Read/Write Functions**

|                                                                                                                                       | 🕘 Variables                                                                                                                   |         |

|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------|

| *u_a1 AD1                                                                                                                             | Variables Structure: One or more scalar - (if you give more than one scalar separate their names and values with spaces or co | mmas)   |

| Add Add [3][4]                                                                                                                        |                                                                                                                               |         |

| scalar parameters : scal1,scal2<br>1.000000e+00. 0.000000e+00.<br>array parameter : ar[2][3][4]<br>ar[0][0][0]:. 0<br>ar[0][0][1]:. 0 | Or Variables       Structure:       Array       Image: Type:       double       horizontal vertical                           |         |

| ar[0][0][2]:. 0<br>ar[0][0][3]:. 0<br>ar[0][1][0]:. 0                                                                                 | File Shocture Edil File                                                                                                       |         |

| ar[0][1][1]:. 0                                                                                                                       | File Structure Edit File                                                                                                      |         |

| ar[0][1][3]:. 0.                                                                                                                      |                                                                                                                               |         |

| ar[0][2][0]:. 0<br>ar[0][2][1]:. 0                                                                                                    |                                                                                                                               |         |

| ar[0][2][2]:, 0.,<br>ar[0][2][3]:, 0.,                                                                                                |                                                                                                                               | Cancel  |

| ar[1][0][0]:. 0                                                                                                                       | ?                                                                                                                             |         |

| ar[1][0][1]:. 0<br>ar[1][0][2]:. 0                                                                                                    |                                                                                                                               |         |

| ar[1][0][3]:. 0<br>ar[1][1][0]:. 0                                                                                                    |                                                                                                                               |         |

| ar[1][1][1]:, 0.,                                                                                                                     |                                                                                                                               |         |

| ar[1][1][2]:, 0.,<br>ar[1][1][3]:, 0.,                                                                                                |                                                                                                                               |         |

| ar[1][2][0]:. 0                                                                                                                       |                                                                                                                               |         |

| ar[1][2][1]:. 0<br>ar[1][2][2]:. 0                                                                                                    |                                                                                                                               |         |

| ar[1][2][3]:. 0                                                                                                                       | Welcome to Inn                                                                                                                | ovation |

|                                                                                                                                       |                                                                                                                               |         |

**EICAS** Automazione S.p.A.

excellence and passion in automatic control design

#### The Converter programmed with ANSI C language

#### **The Input/Output variables**

The input/output variables of the block are defined by means of an appropriate window.

The converters work directly on the output variables of the blocks to which they are connected.

The input variables are then pointers to the output variables to which they are connected .

The input/output variables are ANSI C variables that can be used in any ANSI C function of the block.

excellence and passion in automatic control design

excellence and passion in automatic control design

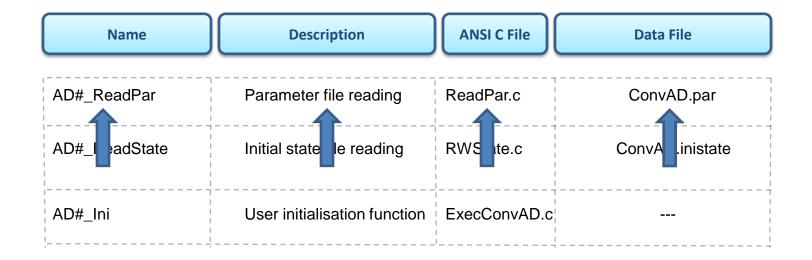

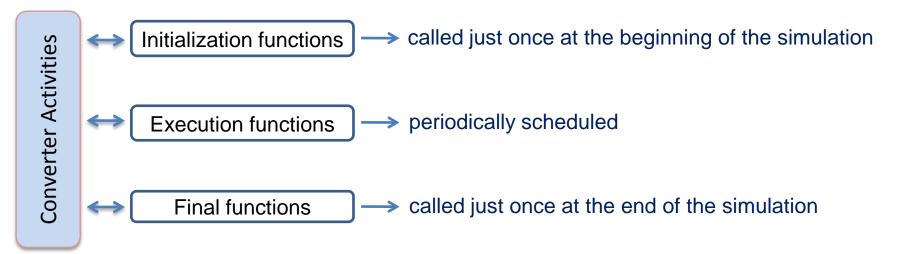

#### The scheduling of the Converter functions The Converter functions

The Converters may be programmed through a set of activities (functions):

**Library** Converter: all the functions are entirely created and managed by EICASLAB.

Converter programmed in **ANSI C**: all the functions have a template provided by EICASLAB and are managed by the user.

The activities are subdivided in three main categories:

excellence and passion in automatic control design

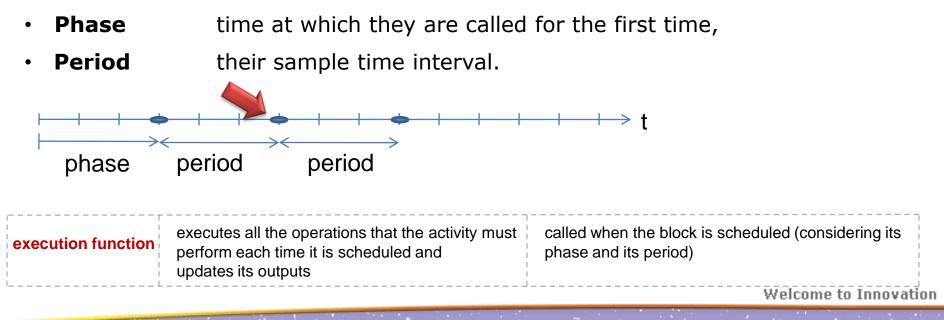

### The scheduling of the Converter functions Scheduling parameters

The user has to fix a **simulation step**,

which represents the time resolution applied in the simulation of the overall project.

The converters are by default istantaneous activities (their duration is negligible with respect to the duration of the other activities).

Their execution functions implement periodic activities characterized by the following scheduling parameters (expressed as a multiple of the simulation step):

excellence and passion in automatic control design

#### The scheduling of the Converter functions

## **Initialization and final functions**

Library converter:

functions entirely created and managed by EICASLAB,

Converters programmed in ANSI C:

functions created by EICASLAB (template) and managed by the user.

The initialization functions are called just once at the beginning of the simulation, in the following order:

- 1) Parameter file reading,

- 2) Initial state file reading,

- 3) User initialisation function (Only when programmed in ANSI C language).

The final functions are called just once at the end of the simulation in the following order:

- 1) User final function (Only when programmed in ANSI C language),

- 2) Final state file writing.

• D/A>

#### **EICAS** Automazione S.p.A.

excellence and passion in automatic control design

#### The scheduling of the Converters

## How to set the scheduling

excellence and passion in automatic control design

he Professional Software Suite for Automatic Control Design and Forecasting